1.1. Introduction

The RISC-V server SoC specification defines a standardized set of capabilities that portable system software such as operating systems and hypervisors, can rely on being present in a RISC-V server SoC.

A server is a computing system designed to manage and distribute resources, services, and data to other computers or devices on a network. It is often referred to as a 'server' because it serves or provides information and resources upon request. Such computing systems are designed to operate continually and have higher requirements for capabilities such as RAS, security, performance, and quality of service. Examples of servers include web servers, file servers, database servers, mail servers, game servers, and more. This specification focuses on defining requirements for general-purpose server computing systems that may be used for one or more of these purposes.

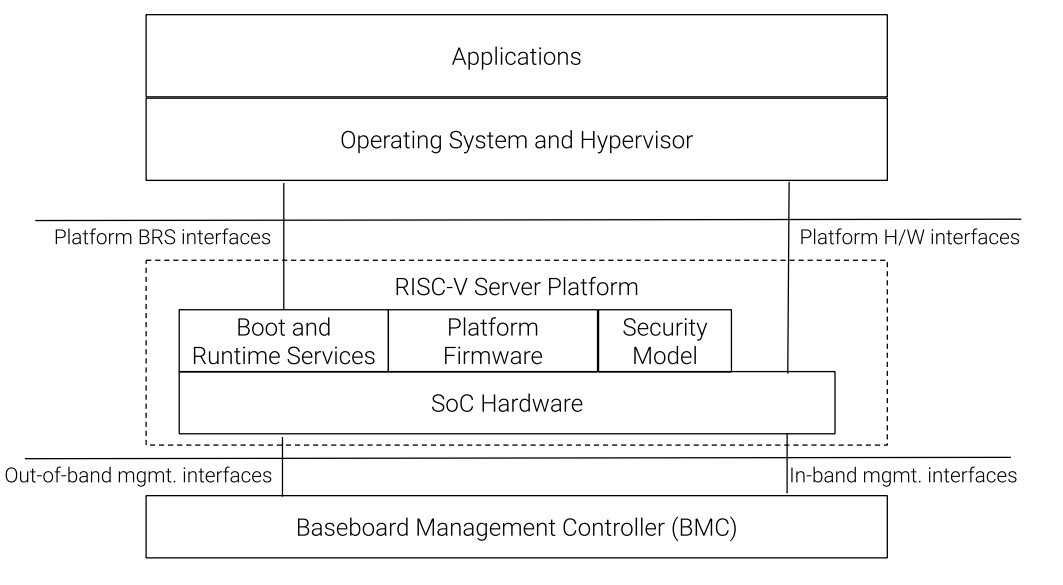

The RISC-V server platform is defined as the collection of SoC hardware, platform firmware, boot/runtime services, and security services. The platform provides hardware interfaces (e.g., harts, timers, interrupt controllers, PCIe root ports, etc.) to portable system software. It also offers a set of standardized RISC-V boot and runtime services [1] based on the UEFI and ACPI standards. To support provisioning and platform management, it interfaces with a baseboard management controller (BMC) through both in-band and out-of-band (OOB) management interfaces. The in-band management interfaces support the use of standard manageability specifications like MCTP, PLDM, IPMI, and Redfish for provisioning and management of the operating system executing on the platform. The OOB interface supports the use of standard manageability specifications like MCTP, PLDM, Redfish, and IPMI for functions such as power management, telemetry, debug, and provisioning. The RISC-V security model [2] includes guidelines and requirements for aspects such as debug authorization, secure/measured boot, firmware updates, firmware resilience, and confidential computing, among others.

The platform firmware, typically operating at privilege level M, is considered part of the platform and is usually expected to be customized and tailored to meet the requirements of the SoC hardware (e.g., initialization of address decoders, memory controllers, RAS, etc.).

This specification standardizes the requirements for the hardware interfaces and capabilities (e.g., timers, interrupt controllers, PCIe root complexes, RAS, QoS, in-band management, etc.) provided by the SoC to software executing on the application processor harts at privilege levels below M. It enables OS and hypervisor vendors to support such SoCs with a single binary OS image distribution model. The requirements posed by this specification represent a standard set of infrastructural capabilities, encompassing areas where divergence is typically unnecessary and where novelty is absent across implementations.

To be compliant with this specification, the SoC MUST support all mandatory rules and MUST support the listed versions of the specifications. This standard set of capabilities MAY be extended by a specific implementation with additional standard or custom capabilities, including compatible later versions of listed standard specifications. Portable system software MUST support the specified mandatory capabilities to be compliant with this specification.

The rules in this specification use the following format:

| ID# | Rule |

|---|---|

CAT_NNN |

The |

A rule or a group of rules may be followed by non-normative text providing context or justification for the rule. The non-normative text may also be used to reference sources that are the origin of the rule. |

|

This specification groups the rules in the following broad categories:

-

Clocks and Timers

-

Interrupt Controllers

-

IOMMU

-

PCIe subsystem

-

Reliability, Availability, and Serviceability

-

Quality of Service

-

Performance monitoring

-

Security

1.1.1. Glossary

Most terminology has the standard RISC-V meaning. This table captures other terms used in the document. Terms in the document prefixed by 'PCIe' have the meaning defined in the PCI Express (PCIe) Base Specification [4] (even if they are not in this table).

| Term | Definition |

|---|---|

ACPI |

Advanced Configuration and Power Interface [5]. |

ACS |

Follows PCI Express. Access Control Services. A set of capabilities used to provide controls over routing of PCIe transactions. |

AER |

Advanced Error Reporting. Follows PCI Express. A PCIe defined error reporting paradigm. |

AIA |

RISC-V Advanced Interrupt Architecture. |

ATS |

Follows PCI Express. Address Translation Services. |

BAR or Base Address Register |

Follows PCI Express. A register that is used by hardware to show the amount of system memory needed by a PCIe function and used by system software to set the base address of the allocated space. |

BMC |

Baseboard Management Controller. A motherboard resident management controller that provides functions for platform management. |

CXL |

Compute Express Link bus standard. |

DMA |

Direct Memory Access. |

DMTF |

Distributed Management Task Force. Industry association for promoting systems management and interoperability. |

ECAM |

Follows PCI Express. Enhanced Configuration Access Method. A mechanism to allow addressing of Configuration Registers for PCIe functions. In addition to the PCI Express Base Specification, see the detailed rules in this specification. |

EP, EP=1 |

Follows PCI Express. Also called Data Poisoning. EP is an error flag that accompanies data in some PCIe transactions to indicate the data is known to contain an error. Defined in PCI Express Base Specification 6.0 section 2.7.2. Unless otherwise blocked, the poison associated with the data must continue to propagate in the SoC internal interconnect. |

GPA |

Guest Physical Address: An address in the virtualized physical memory space of a virtual machine. |

Guest |

Software in a virtual machine. |

Hierarchy ID or Segment ID |

Follows PCI Express. An identifier of a PCIe Hierarchy within which the Requester IDs are unique. |

Host Bridge |

Part of a SoC that connects host CPUs and memory to PCIe root ports, RCiEP, and non-PCIe devices integrated in the SoC. The host bridge is placed between the device(s) and the platform interconnect to process DMA transactions. IO Devices may perform DMA transactions using IO Virtual Addresses (VA, GVA or GPA). The host bridge invokes the associated IOMMU to translate the IOVA to Supervisor Physical Addresses (SPA). |

HPM |

Hardware Performance Monitor. |

Hypervisor |

Software entity that controls virtualization. |

ID |

Identifier. |

IMSIC |

Incoming Message-signaled Interrupt Controller. |

IO Bridge |

See host bridge. |

IOVA |

I/O Virtual Address: Virtual address for DMA by devices. |

MCTP |

Follows DMTF Standard. Management Component Transport Protocol used for communication between components of a platform management system. |

MSI |

Message Signaled Interrupts. |

NUMA |

Non-uniform memory access. |

OS |

Operating System. |

PASID |

Follows PCI Express. Process Address Space Identifier: It identifies the address space of a process. The PASID value is provided in the PASID TLP prefix of the request. |

PBMT |

Page-Based Memory Types. |

PRI |

Page Request Interface. Follows PCI Express. A PCIe protocol that enables devices to request OS memory manager services to make pages resident. |

RCiEP |

Root Complex Integrated Endpoint. Follows PCI Express. An internal peripheral that enumerates and behaves as specified in the PCIe standard. |

RCEC |

Follows PCI Express. Root Complex Event Collector. A block for collecting errors and PME messages in a standard way from various internal peripherals. |

RID or Requester ID |

Follows PCI Express. An identifier that uniquely identifies the requester within a PCIe Hierarchy. Needs to be extended with a Hierarchy ID to ensure it is unique across the platform. |

Root Complex, RC |

Follows PCI Express. Part of the SoC that includes the Host Bridge, Root Port, and RCiEP. |

Root Port, RP |

Follows PCI Express. A PCIe port in a Root Complex used to map a Hierarchy Domain using a PCI-PCI bridge. |

P2P or peer-to-peer |

Follows PCI Express. Transfer of data directly from one device to another. If the devices are under different PCIe Root Ports or are internal to the SoC this may involve data movement across the SoC internal interconnect. |

PLDM |

Follows DMTF standard. Platform Level Data Model. |

PMA |

Physical Memory Attributes. |

PMP |

Physical Memory Protection. |

Significant Cache |

A large cache that might have significant impact on performance. This specification recommendeds that a cache with a capacity larger than 32 KiB be considered a significant cache if it has a significant impact on performance. |

SMBIOS |

System Management BIOS. |

SoC |

System on a chip, also referred as system-on-a-chip and system-on-chip. |

SPA |

Supervisor Physical Address: Physical address used to to access memory and memory-mapped resources. |

SPDM |

Follows DMTF Standard. Security Protocols and Data Models. A standard for authentication, attestation and key exchange to assist in providing infrastructure security enablement. |

SR-IOV |

Follows PCI Express. Single-Root I/O Virtualization. |

TLP |

Follows PCI Express. Transaction Layer Packet. Defined by Chapter 2 of the PCI Express Base Specification. |

QoS |

Quality of Service. Quality of Service (QoS) is defined as the minimal end-to-end performance that is guaranteed in advance by a service level agreement (SLA) to a workload. |

UEFI |

Unified Extensible Firmware Interface. [6] |

UR, CA |

Follows PCI Express. Error returns to an access made to a PCIe hierarchy. |

VM |

Virtual Machine. |